-- Title : USB Controller VHDL listing

-- Project : USB Controller

-- Author : Suryadi W

-- Organization : EE Dept, Bandung Institute of

Technology

-- File : usbsetup

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

setup process of this controller.

-- All basic block needed to build it is defined as

below

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

-- declaration of input and output port

entity usbsetup is

port(

SOP, clock : in bit;

global_reset : in bit;

Serial_in : in bit;

EOP : in bit;

CRC_match : out bit);

end usbsetup;

architecture arch of usbsetup is

-- declaration of component

component shiftreg

port(

D_in, clock, reset : IN BIT;

Q : OUT BIT_VECTOR(7 DOWNTO 0));

end component;

component counter10

PORT (DATA : IN INTEGER RANGE 0 TO 1023;

CLK : IN STD_LOGIC;

CLRN : IN STD_LOGIC;

EN : IN STD_LOGIC;

LD : IN STD_LOGIC;

COUNT : OUT INTEGER RANGE 0 TO 1023);

end component;

component comparator8

PORT(en,clock : IN STD_LOGIC;

p,q : IN STD_LOGIC_VECTOR(7 downto 0);

match : OUT std_logic);

end component;

component comparator2

PORT ( en,clock : IN STD_LOGIC;

p,q : IN STD_LOGIC_VECTOR(3 downto 0);

match : OUT std_logic

bit_match : OUT STD_LOGIC_VECTOR(3 downto 0));

end component;

--for ALL : compat2 use entity work.comparator2

(equations);

component adreg

PORT(clear, store : IN BIT;

d : IN BIT_VECTOR(7 DOWNTO 0);

clk : IN BIT;

q : OUT BIT_VECTOR(7 DOWNTO 0));

end component;

component compmux

PORT(clear, store : IN BIT;

d : IN BIT_VECTOR(7 DOWNTO 0);

clk : IN BIT;

q : OUT BIT_VECTOR(7 DOWNTO 0));

end component;

component comma

PORT ( en,clock : IN STD_LOGIC;

p,q : IN STD_LOGIC_VECTOR(4 downto 0);

match : OUT std_logic);

end component;

component crc5

port ( D, clock : in bit;

reset : in bit;

Q : out bit_vector(0

to 4));

end component;

signal QSR_utama : BIT_VECTOR(7 downto 0);

signal match_utama : bit;

signal match_tujuh : bit;

signal Q_konter : bit_vector(10 downto 0);

signal match_konter :bit;

signal match_1, match_2: bit;

signal bit_match1, bit_match2 : bit_vector (3 downto 0);

signal bantu_1 : bit;

signal bantu_2 :bit;

signal Qic_mux : bit_vector (6 downto 0);

signal ZM : bit;

signal Q_CRC : bit_vector(0 to 4);

BEGIN

U1:shiftreg

port map ( D_in => Serial_in, clock => clock,

reset => global reset;

Q => QSR_utama);

U2:counter10

-- port matching

port map (DATA => DATA, CLK => clock,

CLRN => CLRN, EN => EN, LD => LD,

COUNT => Q_konter);

U3:comparator8

-- synchoronous process

q <= "00000001";

port map (en => en, clock => clock,

p => QSR_utama,

q => q,

match => match_utama);

U4:crc5

port map (D_in => Serial_in,

clock => clock, rst => match_utama,

Q => Q_CRC);

-- determine the validity of incoming packet

compat1:comparator4

q <= "1101";

port map (en => match_utama, clock => clock,

p => QSR_utama(3 downto 0),

q => q,

match => match_1,

bit_match => bit_match1);

compat2:comparator4

q <= "0010";

port map (en => match_utama, clock => clock,

p => QSR_utama(7 downto 4),

q => q,

match => match_2,

bit_match => bit_match2);

bantu_1 <= match_1 xor match_2;

bantu_2 <= bit_match1(2) xor bit_match1(3);

U6:adreg

port map(clear => bantu_2, store => store,

d => QSR_utama,

clk => clk,

q => Qic_mux);

U7:compmux

port map(clear => bantu_2, store => store,

d => QSR_utama,

clk => clk,

q => Qic_mux);

compat3:comparator4

q <= "0000";

port map (en => match_tujuh, clock => clock,

p => QSR_utama(7 downto 4),

q => q,

match => ZM,

bit_match => bit_match);

U9:comma

port map (en => ZM, clock => clock,

p => QSR_utama(7 downto 3),

q => Q_CRC(0 to 4);

match => CRC_match);

end arch;

-- File : dffg

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a

D flip-flop with reset signal

library ieee;

use ieee.std_logic_1164.all;

-- declaration of input and output port

entity dffg is

port ( D,clock,reset : in bit;

Q : out bit );

end dffg;

architecture behave of dffg is

begin

process(reset,clock)

begin

if reset ='1' then

Q <= '0';

elsif clock ='1' and clock'event then -- how we define a rising edge flip-flop

Q<=D;

end if;

end process;

end behave;

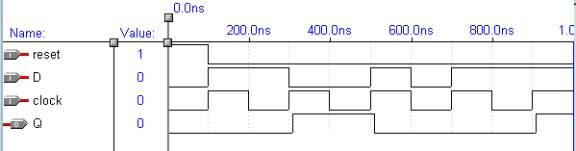

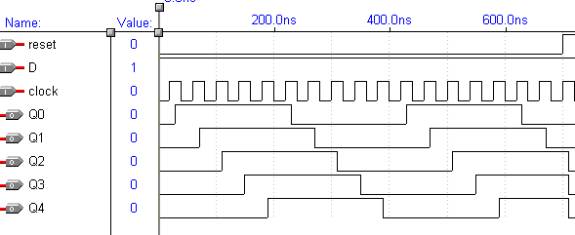

As shown by this timing diagram, the input signal will be passed to output port as long as the reset signal is not asserted. Notice that this is a rising edge triggered flip-flop. This flip-flop will be one of the basic block to build other modules

-- File : shiftreg

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a

shift register

library ieee;

use ieee.std_logic_1164.all;

entity shiftreg is

port ( D_in,clock,reset : in bit;

Q : out bit_vector ( 7 downto 0 ));

end shiftreg;

architecture behave of shiftreg is

-- the description of dffg has been defined as shown above

component dffg

port ( D,clock,reset : in bit ;

Q : out bit);

end component;

signal DS,QS : bit_vector ( 7 downto 0 );

begin

DS(7) <= D_in;

ass1:

for x in 6 downto 0 generate

DS(x) <= QS(x+1);

end generate;

ass2:

for x in 7 downto 0 generate

reg : dffg

port map ( D=>DS(x),clock=>clock,reset=>reset,Q=>QS(x));

end generate;

Q<=QS;

end;

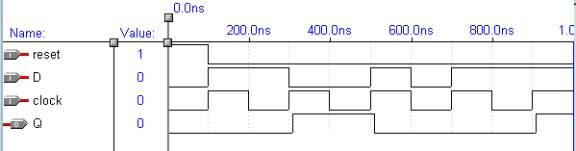

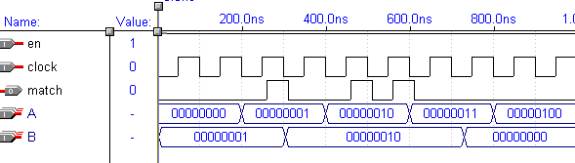

As shown by this timing diagram, the input signal D will be passed to output array Q, each delayed by one clock. This timing diagram is simulated using functional timing simulation, that is all delay caused by wiring or other sources are ignored. The serial data from host must be packaged into packets. This is what this register do.

-- File : counter10

-- copyrights : Altera Corporation

-- version : 9.16 Baseline ( student edition )

-- Description : The below listing describes the

behavioral description of

-- a 10 bit counter

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity counter10 is

port ( data : in integer range 0 to 1023;

clock : in std_logic;

clrn : in std_logic;

en : in std_logic;

ld : in std_logic;

count : out integer range 0 to 1023 );

end counter10;

architecture a of counter10 is

signal count1 : integer range 0 to 1023;

begin

process (clock,clrn)

begin

if clrn='0' then

count1 <= 0;

elsif ( clock'event and clock ='1') then

if ld ='1' then

count1 <= data;

else

if en ='1' then

count1 <=count1+1;

else

count1 <= count1;

end if;

end if;

end if;

end process;

count <= count1;

end a;

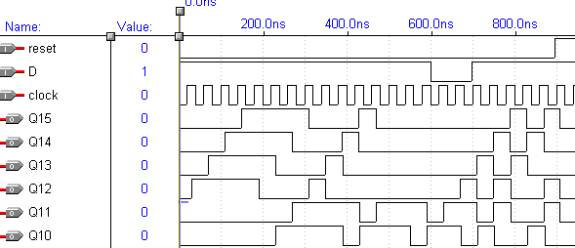

This counter starts counting as soon as there is an

enavle ( en ) signal. This counts how many times the rising edge of clock

appear, as long as the load ( ld ) signal is not asserted. If this two signals (

ld and en ) exist, then the output will count the data signal whose match the

clock

-- File : comp1

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of

one bit comparator

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity comp1 is

port ( en,clock : in bit;

A,B : in bit;

match : out bit );

end comp1;

architecture behave of comp1 is

begin

process ( en,clock )

begin

if ( clock='1' and en ='1') then

if A = B then match <= '1';

else match <='0';

end if;

else match <='0';

end if;

end process;

end behave;

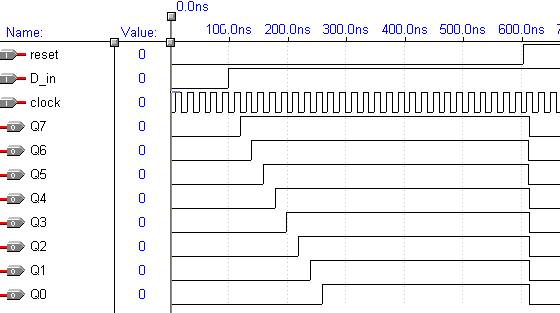

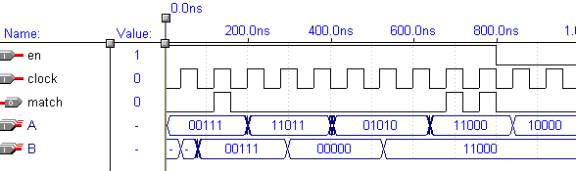

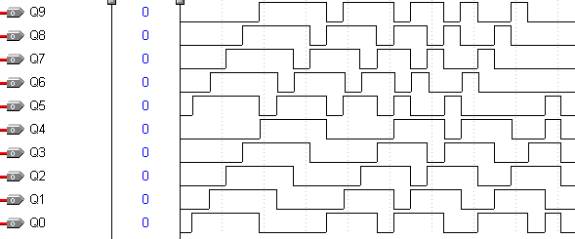

As shown by this timing diagram, as long as the input signal A and B has the same value, a match signal will be asserted. Also note this circuit is actived by enable signal. Some modules, mostly are comparator, will use this block as the building block.

-- File : comparator4

-- Author : Tri Dewi

-- Created : 10 February, 2001

-- Modifier : Suryadi

-- Date : 10 April,2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a 4 bit comparator. It will detect the matching of each bit

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity comparator4 is

port ( en,clock : in bit;

P,R : in bit_vector ( 3 downto 0 );

bit_match : out bit_vector ( 3 downto 0 );

match : out bit );

end comparator4;

architecture behave of comparator4 is

component comp1

port ( en,clock : in bit;

A,B : in bit;

match : out bit );

end component;

signal bit_match_s : bit_vector ( 3 downto 0 );

signal ps,qs : bit_vector ( 3 downto 0 );

begin

ass1:

for x in 3 downto 0 generate

basicb : comp1

port map ( en => en, clock => clock, A => ps(x), B => qs(x),

match => bit_match_s(x));

end generate;

ps <= P ;

qs <= R ;

bit_match <= bit_match_s;

match <= ( bit_match_s(3) and bit_match_s(2) and bit_match_s(1) and

bit_match_s(0));

end behave;

-- File : comparator5

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a 5 bits comparator

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity comparator5 is

port ( en,clock : in bit;

A,B : in bit_vector ( 4 downto 0 );

match : out bit );

end comparator5;

architecture behave of comparator5 is

begin

process ( en,clock )

begin

if ( clock='1' and en ='1') then

if A = B then match <= '1';

else match <='0';

end if;

else match <='0';

end if;

end process;

end behave;

Similar to the above one, but now the input is an array, each containing 5 bit. If the input A and B is match, then the output signal will be asserted. This block will check whether the CRC ( 5 bit ) is correct. Hence, we also need a 16 bit comparator to check the CRC bit ( 16 bit ) for a data packet.

-- File : comparator8

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a 8 bits comparator

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity comparator8 is

port ( en,clock : in bit;

A,B : in bit_vector ( 7 downto 0 );

match : out bit );

end comparator8;

architecture behave of comparator8 is

begin

process ( en,clock )

begin

if ( clock='1' and en ='1') then

if A = B then match <= '1';

else match <='0';

end if;

else match <='0';

end if;

end process;

end behave;

Similar to the above one, but now the input is an array, each containing 8 bit. If the input A and B is match, then the output signal will be asserted.

-- File : comparator16

-- Created : 10 June, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description

-- of a 16 bits

comparator

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity comparator16 is

port ( en,clock : in bit;

A,B : in bit_vector ( 7 downto 0 );

match : out bit );

end comparator16;

architecture behave of comparator16 is

begin

process ( en,clock )

begin

if ( clock='1' and en ='1') then

if A = B then match <= '1';

else match <='0';

end if;

else match <='0';

end if;

end process;

end behave;

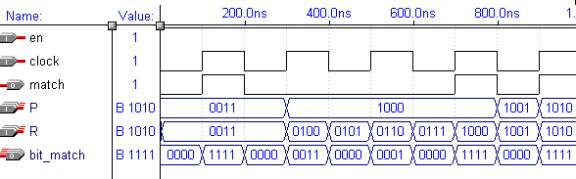

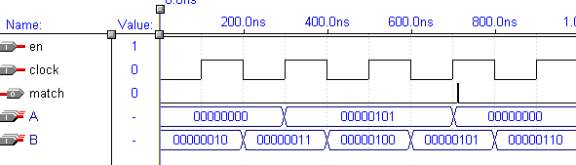

This timing diagram tells us that as long as each bit of A and B are identical, then a match signal will be asserted. This component will be used to detect the CRC bit of data packet

-- File : adreg

-- Author :

Tri Dewi

-- Created : 10 April, 2001

-- Modifier : Suryadi

-- Date :

15 May,2001

-- Last update : June, 2001

-- Description : The below listing describes the

behaviral description

-- of 7 bit address register

library ieee;

use ieee.std_logic_1164.all;

entity adreg is

port ( clock : in bit;

clear, store : in bit;

D : in bit_vector ( 6 downto 0 );

Q : out bit_vector ( 6 downto 0 ));

end adreg;

architecture behave of adreg is

begin

process ( clear,store )

begin

if ( clear = '1' and store ='1') then

if clock ='1' then

Q<=D;

end if;

elsif ( clear ='0' and store ='0') then

Q <="0000000";

end if;

end process;

end behave;

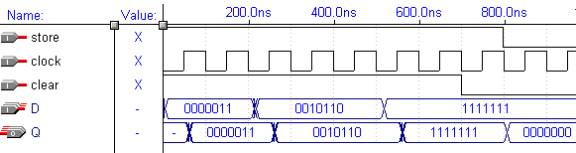

As may be seen from this diagram, as long as the store and clear signal are asserted, the input array will be passed to output. This circuit may implement an address register, for this case, a 7 bit address register. As described above, when a SETUP packet is received correctly, one expect to receive an 8 bytes data packet that contains the newly assigned address. This address will be saved at this register.

-- File : crc5

-- Author : Tri Dewi

--Created : 10 Februay, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description of

-- a CRC 5 bit circuit

library ieee;

use ieee.std_logic_1164.all;

entity crc5 is

port ( D : in bit ;

reset,clock : in bit;

Q : out bit_vector( 0 to 4 ));

end crc5;

architecture behave of crc5 is

component dffg

port ( D,clock,reset : in bit;

Q : out bit );

end component;

signal DS,QS : bit_vector ( 0 to 4 );

begin

DS(0) <= D xor QS(4);

ass1:

for x in 1 to 4 generate

DS(x) <= QS(x-1);

end generate;

ass2:

for x in 0 to 4 generate

reg : dffg

port map ( D => DS(x),clock => clock, reset => reset, Q => QS(x));

end generate;

Q <= QS;

end;

-- File : crc16

-- copyrights : Altera Corporation

-- version : 9.16 Baseline ( student edition )

-- Description : The below listing describes the

behavioral description of

-- a crc 16 bit circuit

library ieee;

use ieee.std_logic_1164.all;

entity crc16 is

port ( D : in bit ;

reset,clock : in bit;

Q : out bit_vector( 0 to 15 ));

end crc16;

architecture behave of crc16 is

component dffg

port ( D,clock,reset : in bit;

Q : out bit );

end component;

signal DS,QS : bit_vector ( 0 to 15 );

begin

DS(0) <= D xor QS(15);

ass1:

for x in 1 to 4 generate

DS(x) <= QS(x-1);

end generate;

DS(5) <= QS(4) xor DS(0);

ass2:

for x in 6 to 11 generate

DS(x) <= QS(x-1);

end generate;

DS(12) <= QS(11) xor DS(0);

ass3:

for x in 13 to 15 generate

DS(x) <= QS(x-1);

end generate;

ass4:

for x in 0 to 15 generate

reg : dffg

port map ( D => DS(x),clock => clock, reset => reset, Q => QS(x));

end generate;

Q <= QS;

end behave;

-- File : mux4

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description of

-- a 4-1 multiplexer

library ieee;

use ieee.std_logic_1164.all;

entity mux4 is

port ( sel : in bit_vector( 1 downto 0 );

A,B,C,D : in bit;

Y : out bit);

end mux4;

architecture behave of mux4 is

begin

process(sel,A,B,C,D)

begin

case sel is

when "00" => Y <=A;

when "01" => Y <=B;

when "10" => Y <=C;

when "11" => Y <=D;

when others => Y <=A;

end case;

end process;

end behave;

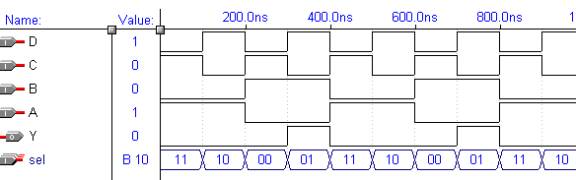

As may be seen from this timing diagram, the input signal will be passed to output, depends on the value of the selector signal. For instance, when the selector signal is 00, then the input signal from input A will be passed to output.

-- File : mux8

-- Created : 10 April, 2001

-- Last update : 14 June, 2001

-- Description : The below listing describes the

behavioral description of

-- a 8-1 multiplexer

library ieee;

use

ieee.std_logic_1164.all;

entity mux8 is

port (

sel

: in bit_vector( 2 downto 0 );

A,B,C,D : in bit;

E,F,G,H : in bit;

Y

: out bit);

end mux8;

architecture behave of

mux8 is

begin

process(sel,A,B,C,D,E,F,G,H)

begin

case

sel is

when

"000" => Y <=A;

when

"001" => Y <=B;

when

"010" => Y <=C;

when

"011" => Y <=D;

when

"100" => Y <=E;

when

"101" => Y <=F;

when

"110" => Y <=G;

when

"111" => Y <=H;

when

others => Y <=A;

end

case;

end process;

end behave;

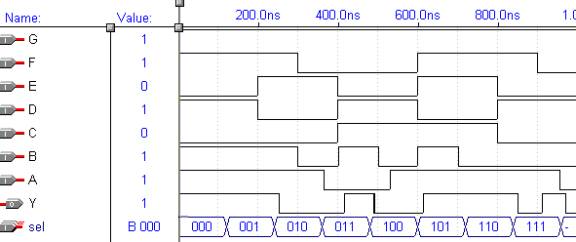

As may be seen from this timing diagram, the input signal will be passed to output, depends on the value of the selector signal. For instance, when the selector signal is 000, then the input signal from input A will be passed to output.